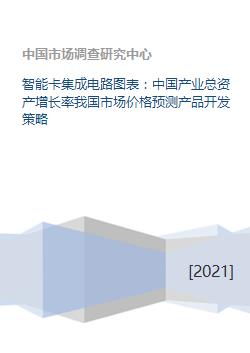

機載雷達作為現(xiàn)代航空電子系統(tǒng)的核心傳感器,其性能直接關系到目標探測、跟蹤、成像與識別的效能。數(shù)據(jù)處理技術是雷達系統(tǒng)的“大腦”,而實現(xiàn)這一“大腦”功能的物理基礎——集成電路,正面臨著諸多嚴峻挑戰(zhàn)。這些挑戰(zhàn)不僅源于雷達任務本身的復雜性,更來自于機載平臺嚴苛的空間、功耗和環(huán)境限制。

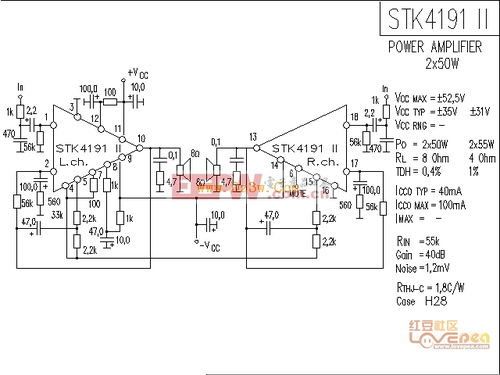

- 極端算力需求與低功耗的矛盾:現(xiàn)代機載雷達,尤其是多功能相控陣雷達,需要實時處理海量數(shù)據(jù)。以合成孔徑雷達(SAR)成像或空時自適應處理(STAP)為例,算法涉及大規(guī)模的矩陣運算與高速傅里葉變換,對計算吞吐量和能效比提出了近乎矛盾的要求。集成電路必須在有限的尺寸和嚴格的散熱條件下,提供每秒萬億次(TOPS)甚至更高的運算能力,同時將功耗控制在數(shù)百瓦以內。這驅動著芯片設計向多核、眾核并行架構以及先進的低功耗工藝(如FinFET、FD-SOI)發(fā)展。

- 高帶寬數(shù)據(jù)接口與存儲瓶頸:雷達接收的回波數(shù)據(jù)速率極高,可達數(shù)十Gbps甚至更高。如何將如此高速的數(shù)據(jù)流可靠地導入處理芯片,并在芯片內部進行高效緩沖和調度,是集成電路設計的關鍵。片上存儲(SRAM)的容量和帶寬往往成為性能瓶頸。設計者需要精妙地平衡存儲器層次結構(如使用高帶寬存儲器HBM)、設計高效的數(shù)據(jù)復用和傳輸通路,以匹配計算單元的數(shù)據(jù)“饑渴”,避免因數(shù)據(jù)等待造成的計算資源閑置。

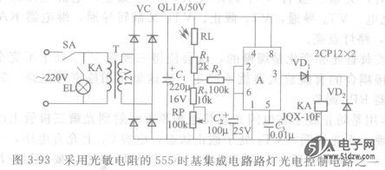

- 算法復雜性與硬件固化(硬化)的權衡:雷達信號處理算法迭代迅速,從傳統(tǒng)的脈沖壓縮、動目標檢測(MTD)到更先進的認知雷達處理,算法靈活性與專用計算效率之間存在固有矛盾。全可編程架構(如高端FPGA、GPU)靈活但能效較低;全定制ASIC能效高但一旦流片即無法更改。因此,當前的主流方向是采用異構集成與可重構計算架構,例如將固定的前端處理(如FFT、濾波)用硬件加速器實現(xiàn),而將高層、易變的算法部分保留在可編程單元(如處理器核或可重構陣列)中,在芯片層面實現(xiàn)軟硬協(xié)同優(yōu)化。

- 惡劣環(huán)境下的可靠性與魯棒性:機載環(huán)境面臨寬溫范圍、劇烈振動、高空宇宙射線輻射等挑戰(zhàn)。這要求集成電路具備極高的可靠性。在芯片設計階段,必須采用抗輻照設計技術、三重模塊冗余(TMR)、誤差檢測與糾正(ECC)電路等,并經(jīng)過嚴格的工藝篩選和可靠性測試。芯片的封裝和散熱設計也需滿足航空級的機械與熱學標準,這些都會增加芯片的設計復雜性和成本。

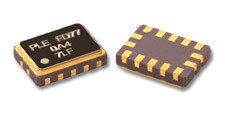

- 小型化、輕量化與系統(tǒng)集成(SoC/SiP)的壓力:機載空間極其寶貴,推動著雷達處理系統(tǒng)向更小、更輕、更集成的方向發(fā)展。片上系統(tǒng)(SoC)和系統(tǒng)級封裝(SiP)技術成為必然選擇。挑戰(zhàn)在于如何將高性能數(shù)字計算核(如CPU、DSP)、模擬/混合信號電路(如ADC接口)、高速串行接口乃至射頻前端模塊,高效、低干擾地集成在同一芯片或封裝內。這涉及到復雜的信號完整性、電源完整性和熱管理問題,對芯片-封裝-系統(tǒng)協(xié)同設計提出了極高要求。

- 設計驗證與測試的復雜性:雷達處理芯片的功能正確性和性能達標與否,直接關系到整個雷達系統(tǒng)的成敗。其驗證場景極其復雜,需要構建從數(shù)字比特流到雷達回波場景的完整閉環(huán)仿真測試環(huán)境。硬件仿真、原型驗證以及最終的板級和系統(tǒng)級測試都耗時耗力且成本高昂。尤其是對算法加速模塊的驗證,需要確保其在所有邊界條件下都能滿足嚴格的實時性與精度指標。

而言,機載雷達數(shù)據(jù)處理集成電路的“難”,本質上是要求在“方寸之間”的硅片上,同時攻克“算得快、吃得少、傳得穩(wěn)、變得巧、靠得住、裝得下”這六大難關。這不僅是半導體技術的挑戰(zhàn),更是雷達系統(tǒng)學、信號處理算法與集成電路設計深度交叉融合的綜合性課題。隨著人工智能與認知處理技術的融入,未來芯片還將需要集成專用的智能處理單元,這又將開辟新的挑戰(zhàn)領域,持續(xù)推動著航空電子集成電路向更高性能、更高智能和更高可靠性的方向發(fā)展。